# State of the art Routers Architecture (Juniper, Cisco, Huawei)

**Octo**ber, 15<sup>th</sup> 2013

Maurizio Ipsale JNCI, CCSI, HCSI

www.klabs.it

## K Labs

- High-quality training courses

- Real-life experience

- Theoretical knowledge

- Plenty of practical hands-on

- Best learning experience

K Labs is a company specialized in Technical Trainings for Telco and ICT market, particularly in the areas of IP data communications, Networking, Optical Transport, Wireless, 2G, 3G and LTE Access Network, DSL, Radio Planning, Traffic Engineering, Security and Testing

**CISCO** Learning Partner

JUNETWORKS Authorized Education Partner

# State of the art Routers Architecture (Juniper, Cisco, Huawei)

www.klabs.it

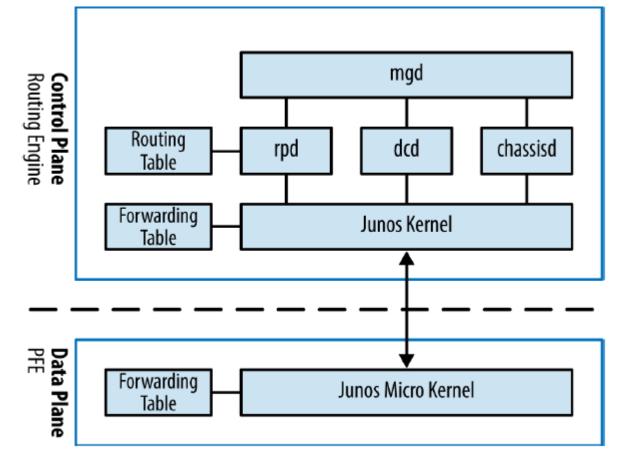

#### **Junos Software Architecture**

- Management daemon (mgd)

- Routing protocol daemon (rpd)

- Device control daemon (dcd)

- Chassis daemon (chassisd)

References:

- 1. Douglas Richard Hanks Jr., Harry Reynolds, Juniper MX Series, O'Reilly Media, Oct 2012

- 2. Antonio Sánchez-Monge, This Week: A Packet Walkthrough on the M, MX, AND T Series, Juniper Networks Books, Jan 2013

Courtesy of Juniper Networks Education Services

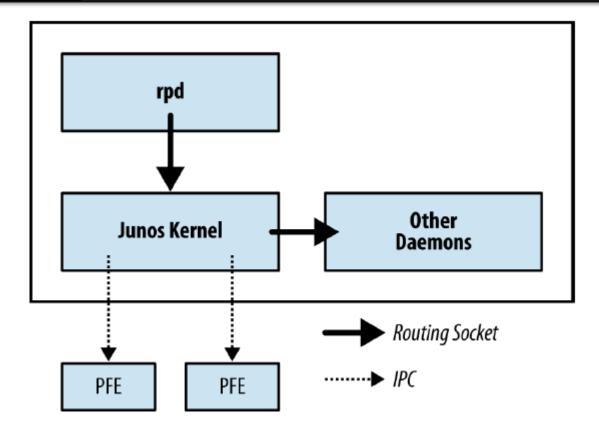

#### **Routing Sockets**

nowledg

Routing sockets are a UNIX mechanism for controlling the routing table. The Junos kernel takes this same mechanism and extends it to include additional information to support additional attributes to create a carrier-class network operating system.

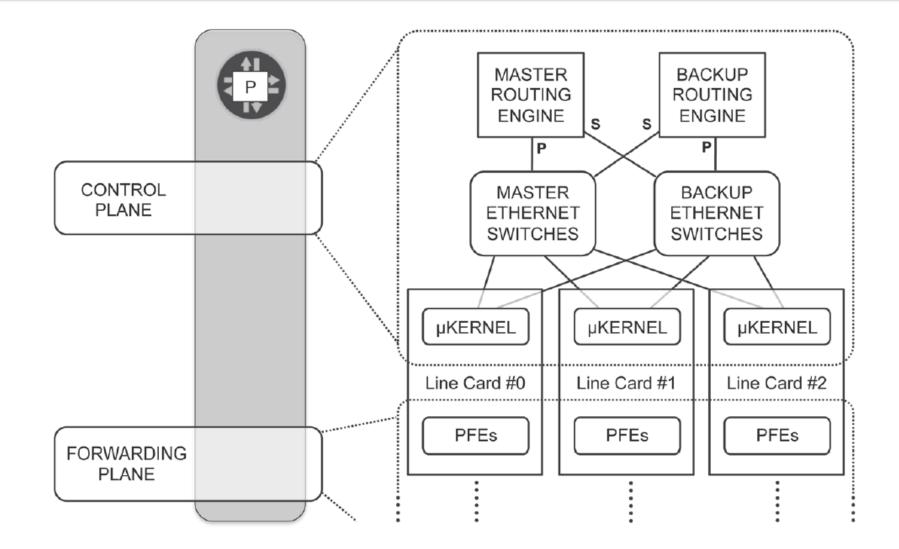

#### **Control Plane**

Klabs

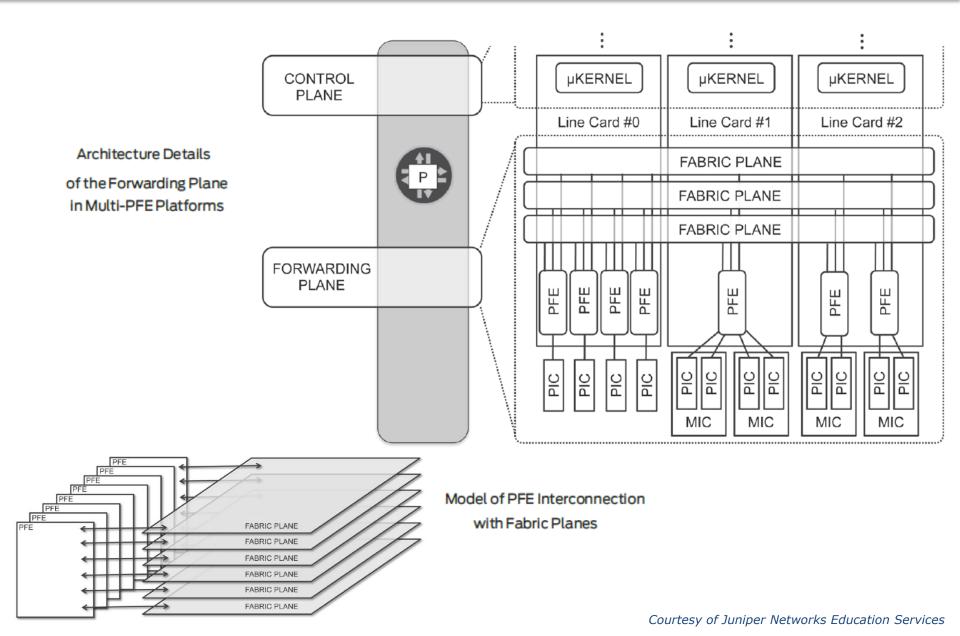

#### **Forwarding Plane**

labs

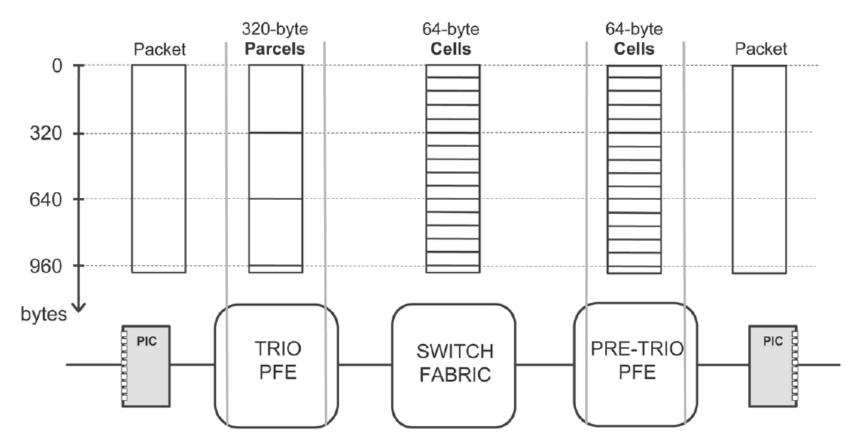

#### **Internal Processing of Transit Packets**

#### INTERNAL OVERHEAD ADDED TO THE CELLS/PACKETS NOT SHOWN FOR SIMPLICITY

Courtesy of Juniper Networks Education Services

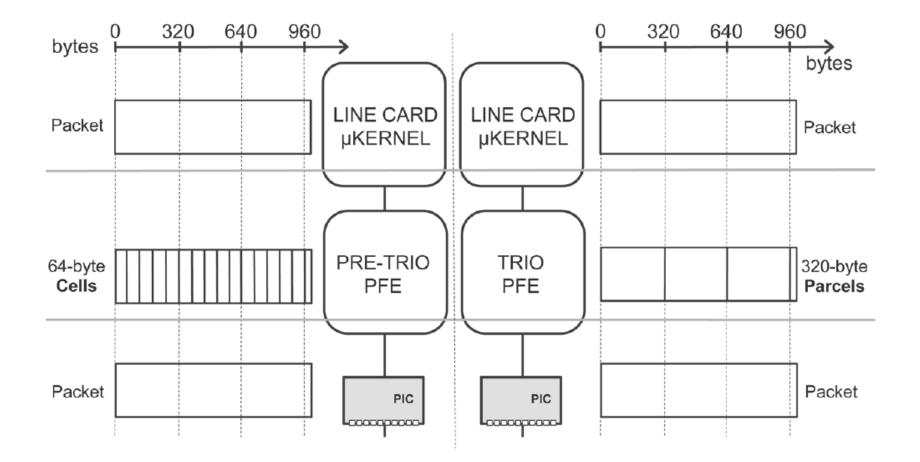

**Internal Processing of Control and Exception Packets**

labs

Courtesy of Juniper Networks Education Services

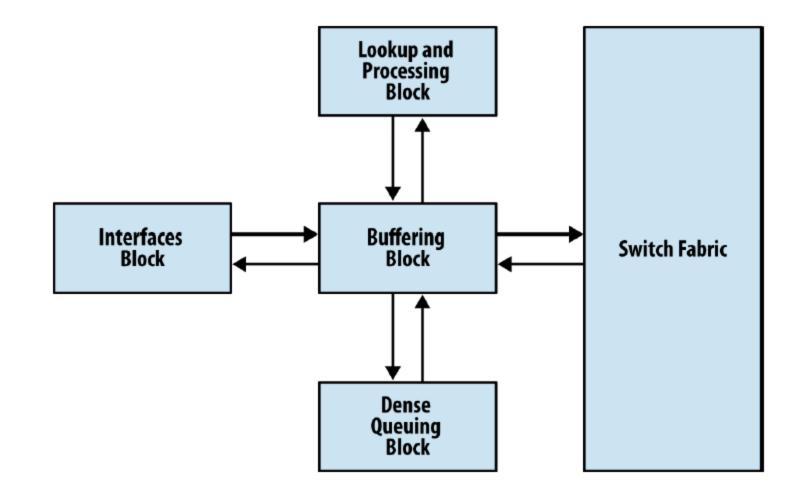

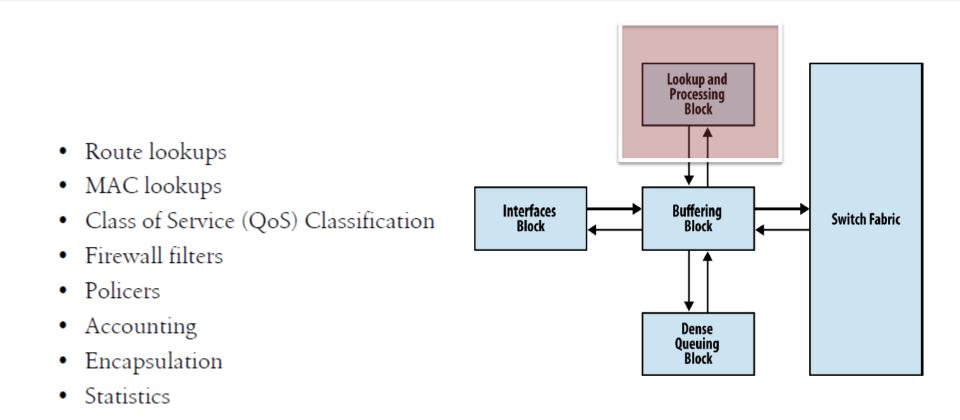

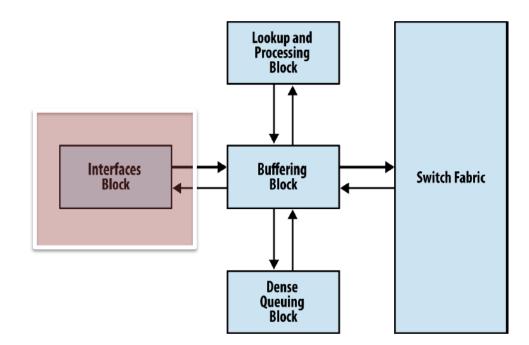

**Trio Functional Block**

Klabs

### **Buffering Block**

Packet Data

labs

- Fabric Queuing

- Revenue Port Queuing

- Delegate Responsibilities:

•Process Oversubscription (<24x1GbE or <2x10GbE on a MIC)

•Revenue Port Queuing (H-QoS)

Courtesy of Juniper Networks Education Services

### **Lookup Block**

•Deep Packet Inspection: 256 bytes into the packet

labs

#### **Interfaces Block**

nowledge

Each packet is inspected at line rate, and attributes such as Ethernet Type Codes, Protocol, and other Layer 4 information are used to evaluate which buffers to enqueue the packet towards the Buffering Block. Preclassification allows the ability to drop excess packets as close to the source as possible, while allowing critical control plane packets through to the Buffering Block.

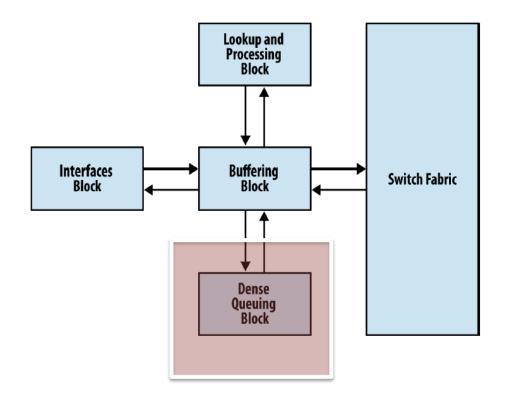

#### **Dense Queuing Block**

nowledge

Depending on the line card, Trio offers an optional Dense Queuing Block that offers rich Hierarchical QoS that supports up to 512,000 queues with the current generation of hardware. This allows for the creation of schedulers that define drop characteristics, transmission rate, and buffering that can be controlled separately and applied at multiple levels of hierarchy.

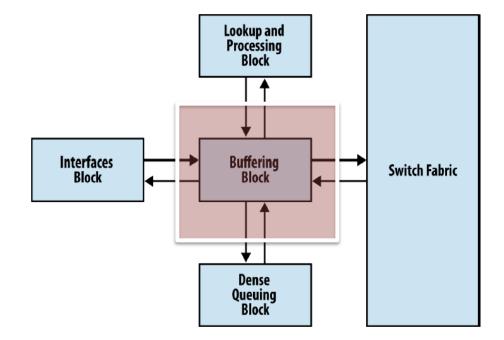

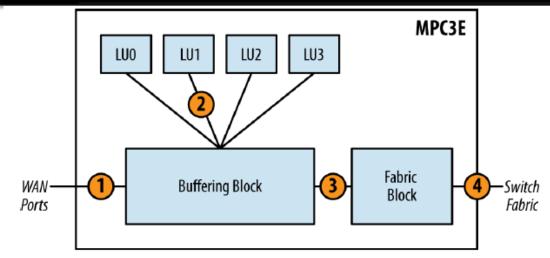

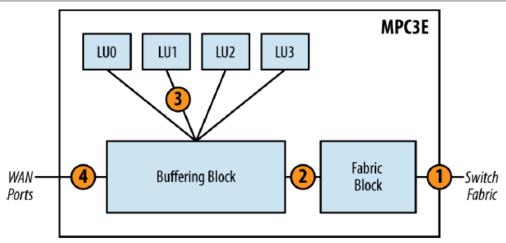

### MPC3E Packet WalkThrough: Ingress

- The packet enters the Buffering Block from the WAN ports and is subject to preclassification. Depending on the type of packet, it will be marked as high or low priority. The Buffering Block will enqueue the packet as determined by the preclassification at service the high-priority queue first. A Lookup Block is selected via round-robin and the packet is sent to that particular Lookup Block.

- The packet enters the Lookup Block. A route lookup is performed and any services such as firewall filters, policing, statistics, and QoS classification are performed. The Lookup Block sends the packet back to the Buffering Block.

- 3. The packet is sent back to the Fabric Block and is enqueued into the switch fabric where it will be destined to another PFE. If the packet is destined to a WAN port within itself, it will simply be enqueued back to the Interfaces Block.

- 4. The packet is sent to the switch fabric.

nowledge

nowledg

- 1. The packet is received from the switch fabric and sent to the Fabric Block. The Fabric Block sends the packet to the Buffering Block.

- The packet enters the Buffering Block. The packet will then be subject to scheduling, shaping, and any other class os service as required. Packets will be enqueued as determined by the class of service configuration. The Buffering Block will then dequeue packets that are ready for transmission and send them to a Lookup Block selected via round-robin.

- The packet enters the Lookup Block. A route lookup is performed as well as any services such as firewall filters, policing, statistics, and QoS classification. The Lookup Block sends the packet back to the Buffering Block.

- The Buffering Block receives the packet and sends it to the WAN ports for transmission.

#### Klabs **Switch and Control Board** {master} dhanks@R1-RE0> show chassis ethernet-switch **Control Board Routing Engine** Displaying summary for switch 0 SSD Link is good on GE port 1 connected to device: FPC1 CPU HDD 24x1GE Speed is 1000Mb Switch Duplex is full Memory Link is good on GE port 2 connected to device: FPC2 Switch Speed is 1000Mb Fabric Duplex is full Ethernet Switch Fabric FPC0 24x1GE GE Link is good on GE port 12 **Routing Engine** Ethernet FPC1 connected to device: Other RE Switch GE Speed is 1000Mb Duplex is full SCB1 FPC2 FPC3 Link is good on GE port 13 24x1GE GE connected to device: RE-GigE **Routing Engine** Ethernet Speed is 1000Mb FPC4 GE Switch Duplex is full SCB0 **FPCN** Courtesy of Juniper Networks Education Services

#### MX2020

| MX2020                                                                                                         |                                                                  | PDM3      |       |       |       |       |       |       |       |                                  |                            |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|-------|----------------------------------|----------------------------|

| FPC10<br>FPC11<br>FPC12<br>FPC13<br>FPC13<br>FPC13<br>FPC13<br>FPC15<br>FPC16<br>FPC16<br>FPC18<br>FPC19       | Upper Backplane                                                  | PSM9      | PSM10 | PSM11 | PSM12 | PSM13 | PSM14 | PSM15 | PSM16 | PSM17                            | Power<br>Supply<br>Modules |

| (B-REO<br>5FB0<br>5FB1<br>5FB1<br>5FB3<br>5FB3<br>5FB3<br>5FB3<br>5FB3<br>5FB3<br>5FB3<br>5FB7<br>5FB7<br>5FB7 | Control Boards,<br>Routing Engines, and<br>Switch Fabric Boards. | PDM2 PDM1 |       |       |       |       |       |       |       | Power<br>Distribution<br>Modules |                            |

| FPC1<br>FPC1<br>FPC3<br>FPC4<br>FPC6<br>FPC6<br>FPC6<br>FPC6                                                   | Lower Backplane                                                  | PSMO      | PSM1  | PSM2  | PSM3  | PSM4  | PSM5  | PSM6  | PSM7  | PSM8                             | Power<br>Supply<br>Modules |

|                                                                                                                |                                                                  |           | PDMO  |       |       |       |       |       |       |                                  |                            |

Courtesy of Juniper Networks Education Services

# State of the art Routers Architecture (Juniper, <u>Cisco</u>, Huawei)

www.klabs.it

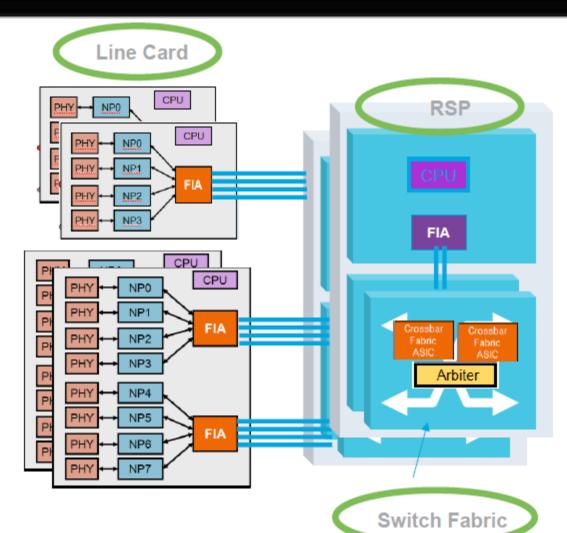

### **Cisco ASR 1000 Building Blocks**

Fully Distributed Architecture for High Performance and High Multidimensional Control Plane Scale

abs

- Data forwarding is fully distributed on the line cards

- Control plane split among RSP and LC CPU (same type of CPU as RSP)

- L2 protocols, BFD, CFM, Netflow runs on the LC CPU for high scale

#### True Modular OS for HA and Operational Simplicity

- Micro-kernel based, true modular OS

- High availability and System stability

- SW patch granularity for operational simplicity

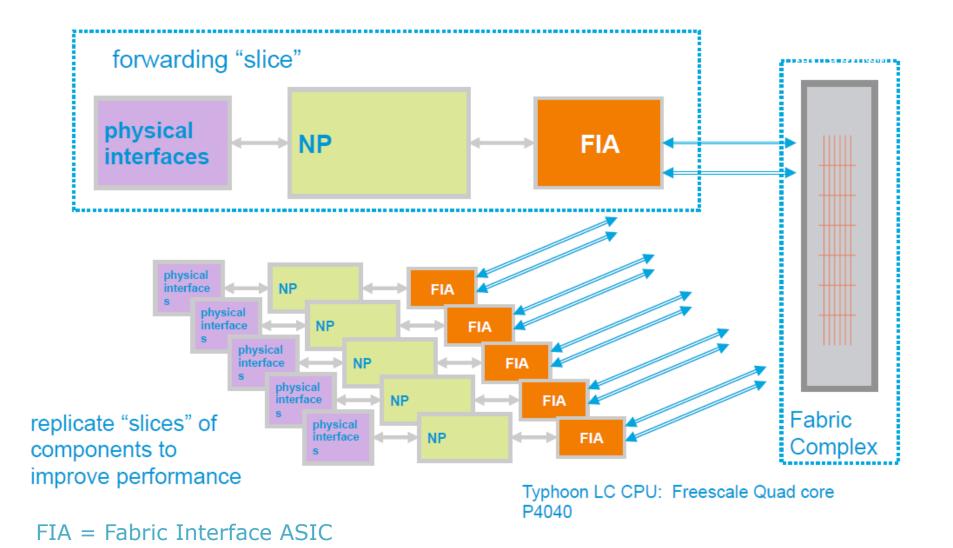

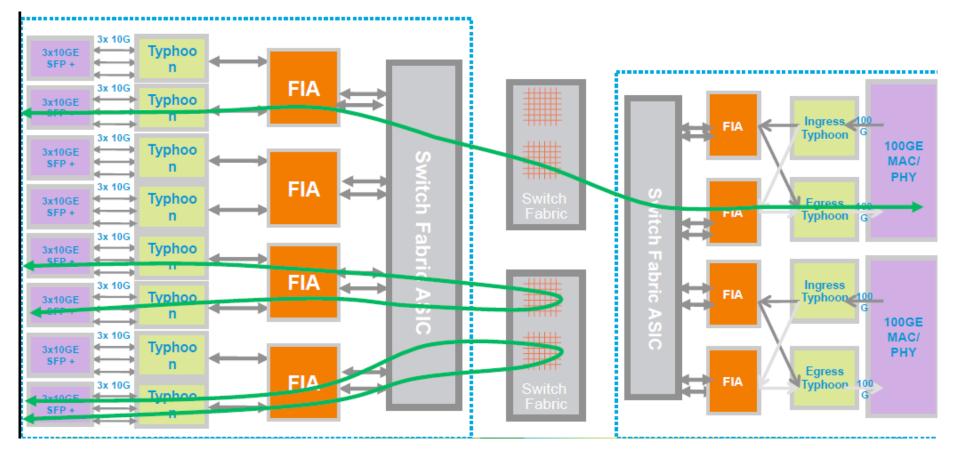

- FIA = Fabric Interface ASIC

#### Active-Active Switch Fabric Guarantee "0" packet loss during RSP failover

#### **Generic RSP Enging Architecture**

Klabs

#### **Generic Line Card Architecture**

#### **Packet Flow Overview**

#### References:

- 1. Cisco Nexus 7000 Hardware Architecture, Cisco Live! 2012

- Xander Thuijs, Understanding Cisco ASR 9000 Series Aggregation Services Routers Platform Architecture and Packet Forwarding Troubleshooting, Cisco Support Community Expert Series Webcast 2013

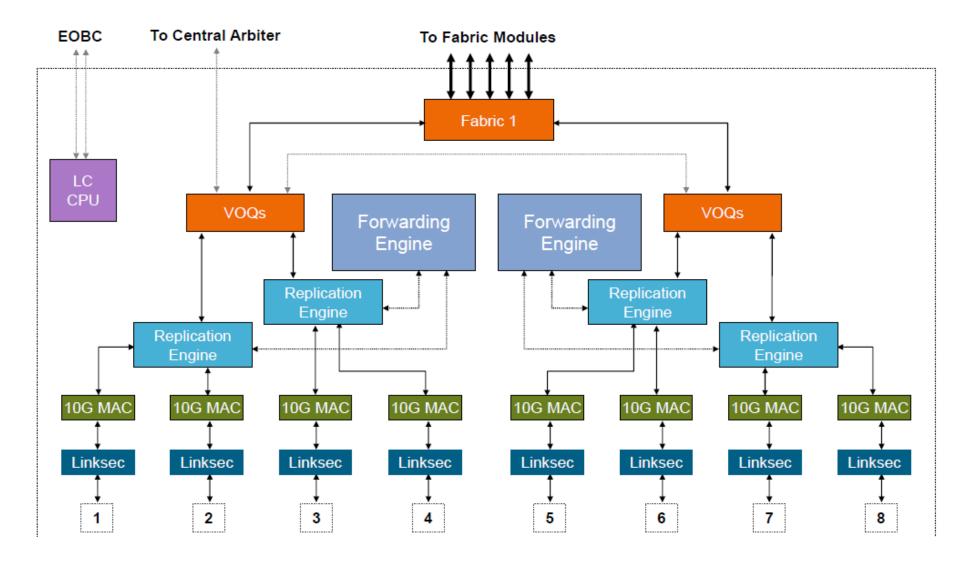

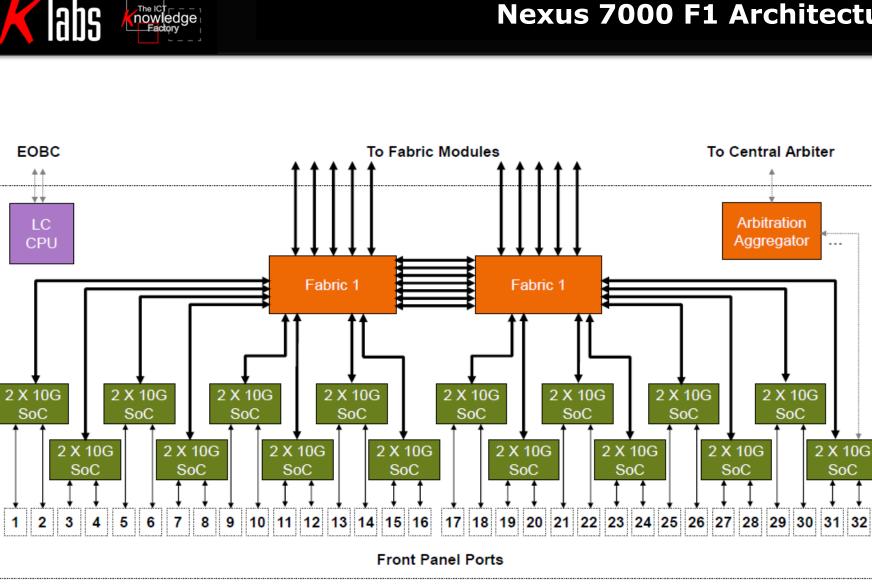

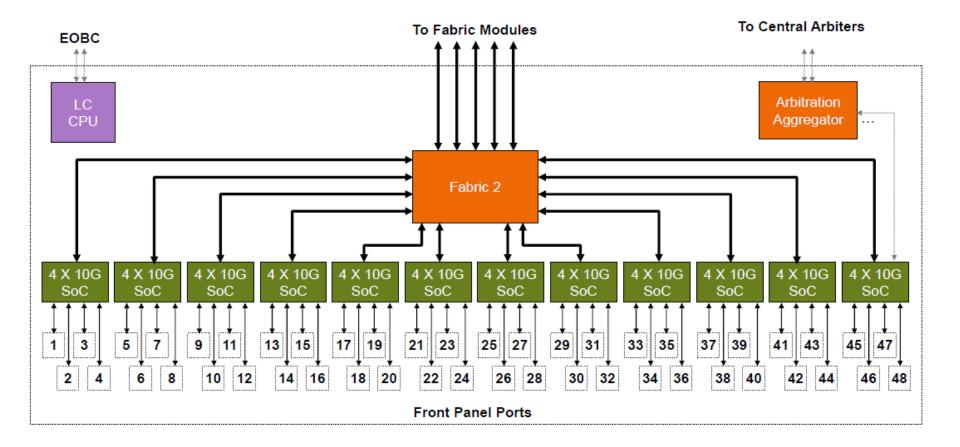

#### **Nexus 7000 M1 Architecture**

....

labs

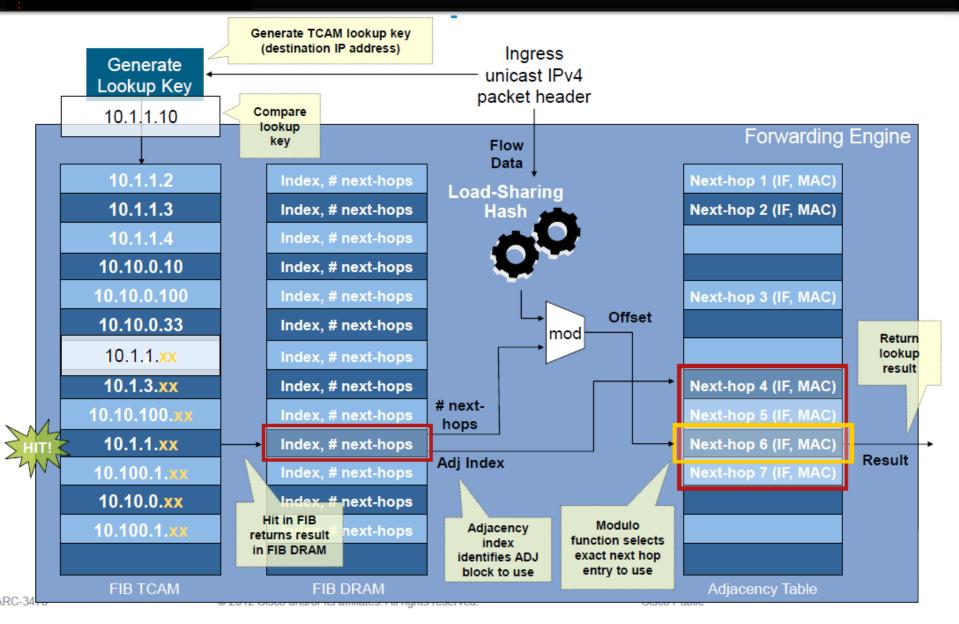

Nexus 7000 decouples control plane and data plane

Forwarding tables built on control plane using routing protocols or static configuration

-OSPF, EIGRP, IS-IS, RIP, BGP for dynamic routing

- Tables downloaded to forwarding engine hardware for data plane forwarding

- -FIB TCAM contains IP prefixes

-Adjacency table contains next-hop information

- FIB TCAM lookup based on destination prefix (longest-match)

- FIB "hit" returns adjacency, adjacency contains rewrite information (nexthop)

- Pipelined forwarding engine architecture also performs ACL, QoS, and NetFlow lookups, affecting final forwarding result

#### **IPv4 FIB TCAM Lookup**

**K** labs

# State of the art Routers Architecture (Juniper, Cisco, <u>Huawei</u>)

www.klabs.it

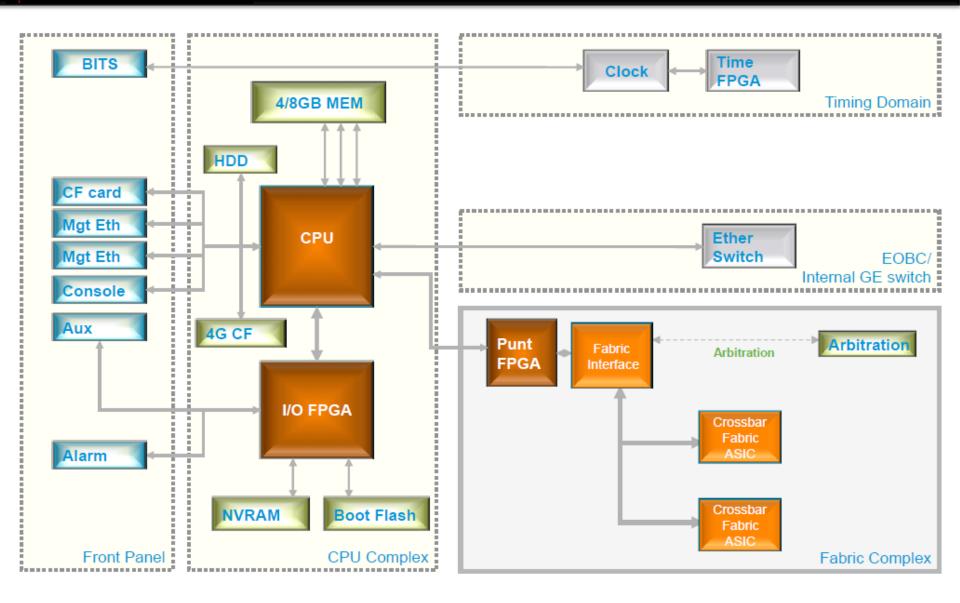

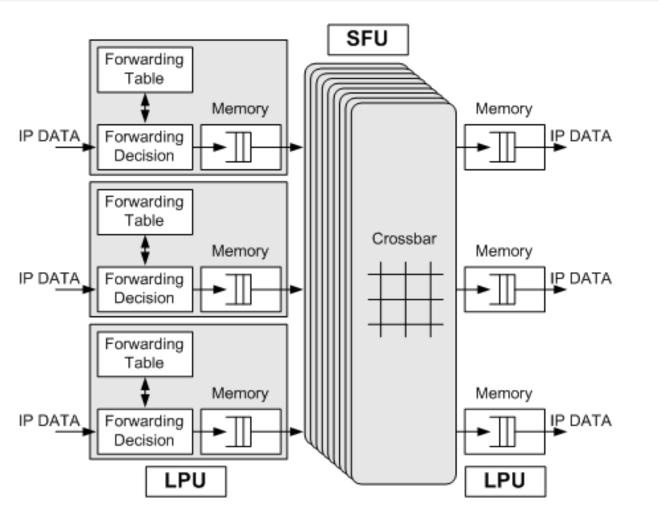

System Control and Management Unit

•Route calculation: All routing protocol packets are sent by the forwarding engine to the MPU for processing. In addition, the MPU broadcasts and filters packets, and downloads routing policies from the policy server.

•Outband communication between boards: The LAN switch modules integrated on the MPU provide outband communications between boards. In this manner, messages can be controlled, maintained, and exchanged between SFUs and LPUs.

•Device management and maintenance: Devices can be managed and maintained through the management interfaces (serial interfaces) provided by the MPU.

•Data configuration: The MPU stores configuration data, startup files, charging information, upgrade software, and system logs.

•Data storage: The MPU provides two interfaces for CF cards, which serve as mass storage devices to store data files.

#### References:

**K** labs

1. HUAWEI NetEngine5000E Core Router, NE5000E Product Description, 2011

Courtesy of Huawei Education Services

now

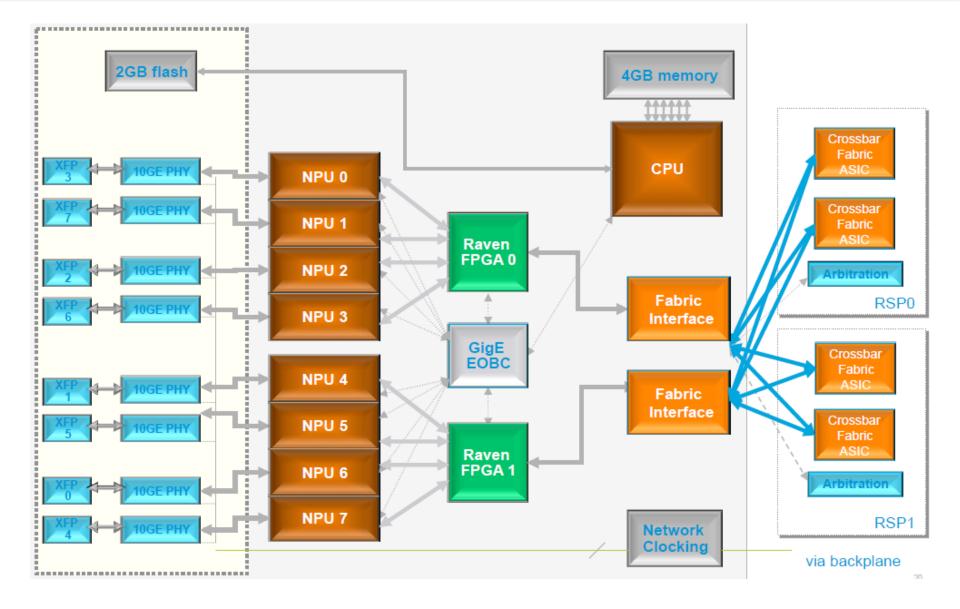

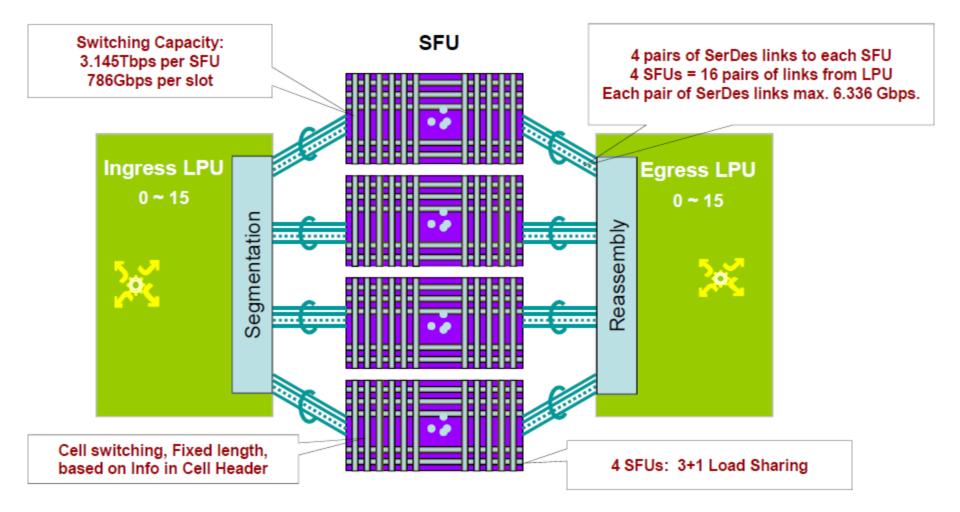

The Switch Fabric Unit B(SFUI-200-B) is the new generation switch board. It supports 200G full duplex capacity per slot. The Switch Fabric Unit B(SFUI-200-B) switches data for the entire system at line speed of 3.15 Tbit/s. This ensures a non-blocked switching network.

The NE40E-X16 has four SFUs working in 3+1 load balancing mode. The entire system provides a switching capacity at wire speed of 12.58 Tbit/s.

The four SFUs load balance services at the same time. When one SFU is faulty or being replaced, the other three SFUs automatically take over its tasks to ensure normal delivery of services.

### Switching Fabric of NE5000E-X16

FIA = Fabric Interface ASIC

**Octo**ber, 15<sup>th</sup> 2013

Maurizio Ipsale JNCI, CCSI, HCSI

www.klabs.it